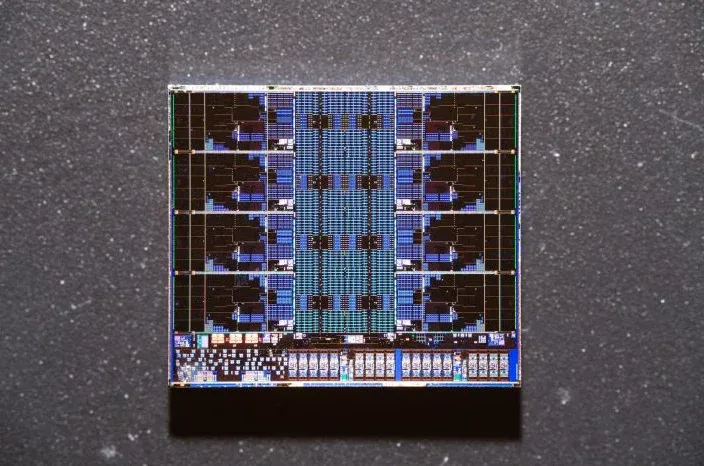

With the release of AMD’s latest 3D V-Cache CPUs, many were curious why the company didn’t extend the additional cache to all CCDs (Core Chiplet Dies). The answer isn’t technical but economic.

The Current 3D V-Cache Design

AMD’s newest Zen 5 3D V-Cache lineup, featuring the Ryzen 9 9950X3D and Ryzen 9 9900X3D, showcases a dual-CCD layout.

While these CPUs deliver notable performance gains, the 3D V-Cache is applied to only one of the CCDs. Here’s why:

-

Technical Feasibility: AMD confirmed there are no technical barriers to integrating 3D V-Cache on both CCDs.

-

Economic Concerns: Adding 3D V-Cache to all CCDs would significantly increase production costs, making the processors less viable for the consumer market.

-

Limited Gaming Benefits: Games benefit more from the leap from 32 MB to 96 MB of L3 cache on one CCD than they would from a dual 3D V-Cache setup.

Challenges with Dual 3D V-Cache

Even though AMD tested processors with dual 3D V-Cache configurations, they decided against releasing them due to:

Thread Scheduling Issues: Efficiently scheduling threads across CCDs becomes challenging.

Threads would ideally need to remain on the cores with 3D V-Cache to maximize performance, which dynamic scheduling complicates.

Cost vs. Performance: The performance gains from dual 3D V-Cache don’t justify the additional cost, especially for gaming.

What the Future Holds

AMD hinted that while dual 3D V-Cache CPUs might not be suitable for the consumer market, they could appear in specialized applications where performance outweighs cost concerns.

For now, AMD’s single-CCD 3D V-Cache design strikes the best balance between performance and affordability.